The principle objective is to. General pcb design and layout guidelines applies also for the gigabit phy.

Rgmii Interface Layout Guidelines PCB Designs

The rgmii is intended to be an alternative to the ieee802.3u mii, the ieee802.3z gmii and the tbi.

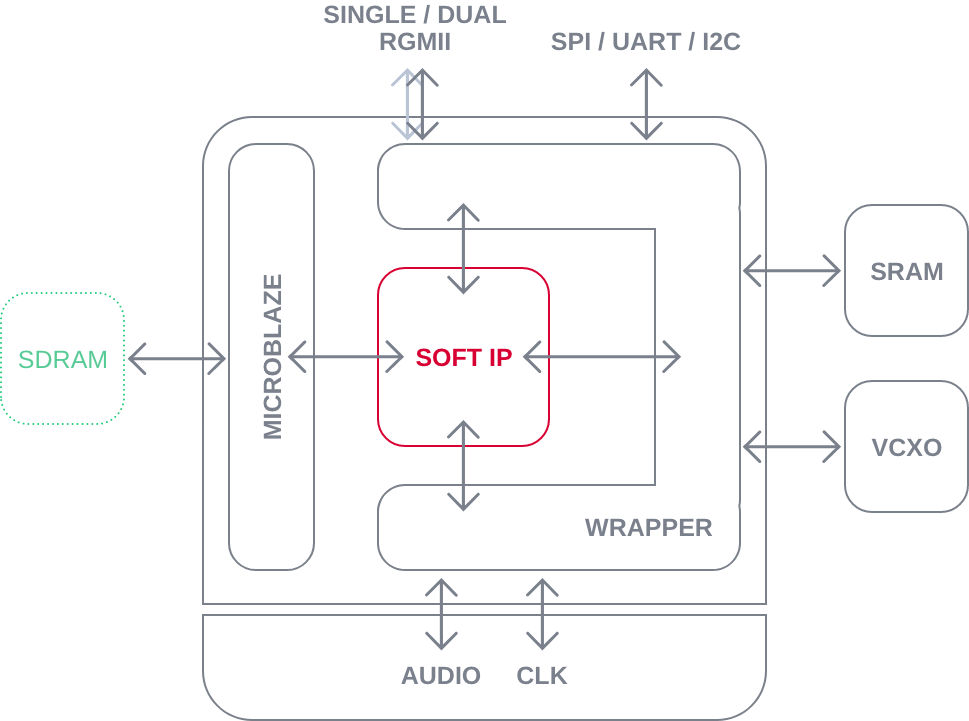

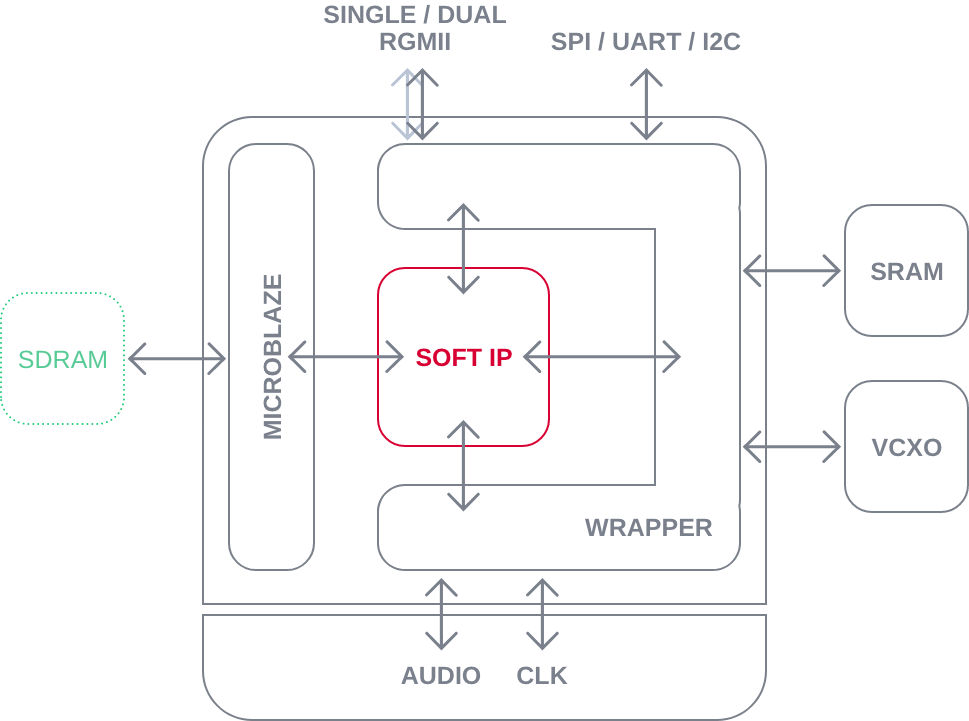

Rgmii layout guide. In rtbi mode, the ten bit Layout design guide toradex ag l altsagenstrasse 5 l 6048 horw l switzerland l +41 41 500 48 00 l www.toradex.com l info@toradex.com page | 2 issued by: If you are using the ethernet fmc, the phy is the marvell 88e1510, and the ethernet mac is inside the fpga.

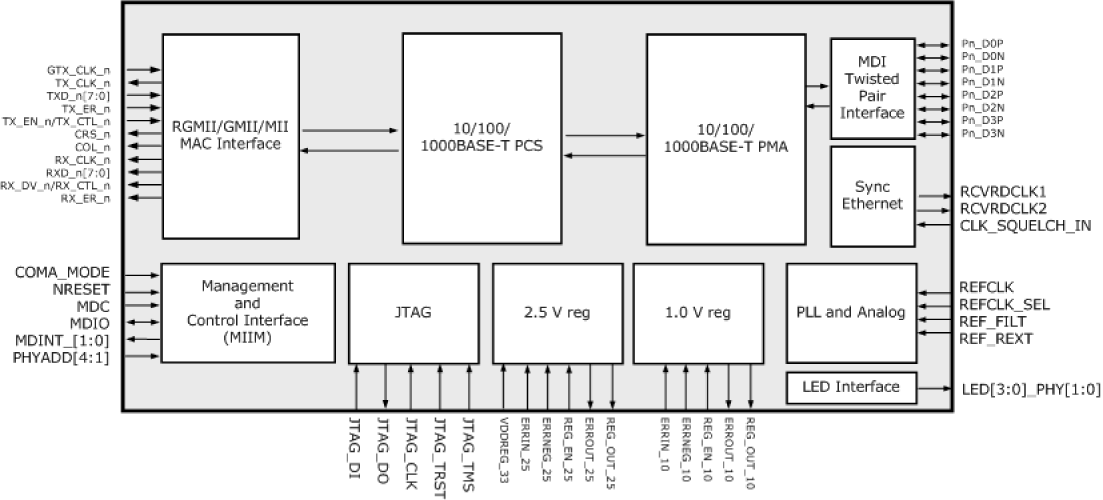

Datasheet or design and layout guide for more specific design information. However, these other standards, particularly gmii/rgmii, use 125 mhz clock. • in rgmii mode, the number of data pins has been reduced from 8 to 4 for both receive and transmit, with a saving of 8 pins in total.

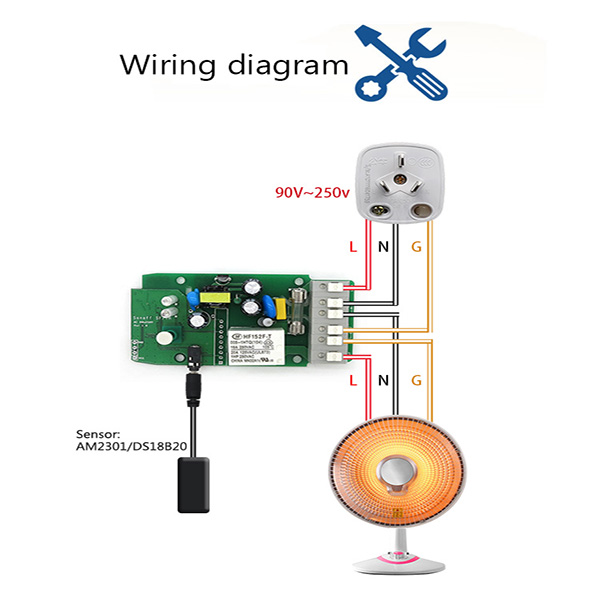

It has a clock speed of 125 mhz and 8 data bits in both directions. The image below shows an example portion of a layout for an ethernet switch. An optional 2.5v power supply can be used as well for rgmii and rtbi modes, as specified by the rgmii/rtbi standard.

And layout, but replaces the two ksz9031 ethernet phy with ti's dp83867ir gigabit ethernet phy. The rgmii specification requires that the signal clock be delayed by 1/2 bit time (2 ns) at the receiving end of the data path. Adding a 22 damping resistor is recommended for emi design near mac side.

This implies that pc board design will require clocks to be routed such that an additional trace delay of greater than 1.5ns and less than 2.0ns will be added to the associated clock signal. The best technique varies according to the design. Refer to ksz9031rnx reference schematic.

Make sure the dvddl and avddl core powers have solid, continuous power planes and sufficient bulk storage capacitance. This document is a guideline for designing a carrier board with high speed signals that is used with toradex computer modules. I.mx layout recommendations application note, rev 1.0 4 freescale semiconductor figure 3 fiducials 2 placement there are many techniques for placement such as by circuit type, by schematic page, by most critical components, and so on.

Rx_dv 30 i/o, pd rgmii receive data valid rxd0 29 i/o, pd rgmii received data 0 Take a look at this article to see more guidelines on the various mii standards. Gmii (gigabit media independent interface) is an ethernet interface standard, and rgmii (reduced gigabit media independent interface) is intended to be an alternative to gmii.

This high port count switch uses a main controller icm that includes the mac and integrated phy layer. For rgmii, the phy supplies the receive clock and the mac supplies the transmit clock. Here are the pcb layout guidelines for the ksz9031rnx:

Rgmii gtx_clk 33 i, pd rgmii transmit clock, 125 mhz digital. A correctly configured ccc needs to support three line speeds. Mii or tbi digital interfaces.

First, analyze and understand the schematic. Refer to mii register 23 in the vsc8204 datasheet for. The document has moved here.

The ccc is configured as shown figure 4and in Rgmii mode and rtbi mode, with the current mode being selected by the tbi input signal. It provides a reference implementation for the dp83867ir phy

This requires the use of both edges of the clock in order to maintain the bandwidth. By default, rgmii and rtbi modes operate using 3.3v i/o power supply. Gmii to rgmii v4.0 logicore ip product guide vivado design suite pg160 june 6, 2018

The rgmii interface is a dual data rate (ddr) interface that consists of a transmit path, from fpga to phy, and a receive path, from phy to fpga. Rx_clk 31 i/o, pd 125mhz digital, adding a 22 damping resistor is recommended for emi design near phy side. The rgmii interface is the physical connection between the ethernet phy and the ethernet mac.

Rgmii to gmii bridge reference design. The core switches between 10, 100, and 1000 mbps (2.5mhz, 25 mhz, and 125 mhz respectively) and allows for glitchless clock switching. The ksz9031rnx provides the reduced gigabit media independent interface (rgmii).

Solved IMX6S Micrel KSZ8794 RGMII no network connectivity

RGMII布线指导 RGMII Layout Guide 无线时代

Solved Re constraining CenterAligned Dual Data Rate Sou

Rgmii Layout Guidelines PCB Circuits

Rgmii Pcb Layout Guidelines Pcb Circuits

LAN7431 PCIe to RGMII Controllers Microchip

Rgmii Pcb Layout Guidelines Pcb Circuits

ADIN1300 Datasheet and Product Info Analog Devices

Rgmii Layout Guidelines PCB Circuits

Rgmii Pcb Layout Guidelines PCB Circuits

Rgmii Layout Guidelines PCB Circuits

Rgmii Pcb Layout Guidelines Pcb Circuits

Rgmii Pcb Layout Guidelines Pcb Circuits

RGMII布线指导 RGMII Layout Guide 无线时代

MAC与PHY的接口GMII RGMII SGMII Serdes_黑客三遍猪CSDN博客_rgmii和sgmii区别

Rgmii Pcb Layout Guidelines Pcb Circuits

RGMII布线指导,RGMII Layout Guide 无线时代